# RESEARCHES REVIEW OF OPTIMIZATION OF ASSEMBLY LINE OF PRINTED CIRCUIT BOARD FOR IMPROVEMENT

Kamal Alzameli, Doctoral Candidate, Dr. Daw R. Alwerfalli, Professor Lawrence Technological University, Southfield, Michigan

**Abstract-** The goal of this paper is to understand and assess the most significant research that helps researchers in academic or industrial field about optimizing the assembly line of printed circuit board for improvement. Background information is categorized based on a related research topic and the most relevant subjects of optimizing PCB assembly line. This paper also includes comparing researches that are related to each other.

\_\_\_\_\_

Key words- printed circuit board, simulation, PCB, Optimization, Scheduling methodology, Placement of Components

---- .

# **1 INTRODUCTION**

It is known that Paul Eisler is the one who invented the printed circuit boards in 1936, but in reality its origins lie nearly 50 years before that. Even though he did not invent the PCB, he made a significant contribution in which he made the challenge shift from a small-scale to a full-scale production. Eisler managed to spotlight the PCB to the world and if it wasn't for him, the work of previous inventors would have not been recognized. [11] A combination of people was responsible for the invention of the brain of electronic devices, the PCB. The origin of contemporary PCBs lies in the world of art rather than technology. It began when Baynes published a patent in 1888 which was intended specifically for the world of art. Then came Hanson in 1903 who contributed to the inventory of PCBs by his idea of producing double-sided through hole circuitry, multilayer circuitry, and a highdensity circuitry. Later on, the process was modified to the manufacture of electronic circuits by Berry in 1913. A significant inventor, Charles Ducas in 1925, made various variations based on a theme which was discovering another method of producing electrical conductors. The formal introduction of PCBs were made when Frederick Seymour in 1927 published a generic patent that deals with the manufacture of flexible circuits solely; in addition, he presented the model of three-dimensional circuitry. Modern PCBs success was due to the various people whom contributed the invention and development of PCBs. [11]

Therefore, the argument of which one first patent for the PCB is between Eisler 1936 and Baynes 1888 and it all depends on which way you want to look at it. From a theory perspective, Baynes is the first one who patent for the PCB, but if you look at the real PCB board and wonder who put it together and made it function then Eisler is the first person who innovated the PCB.

Electronic modules are found in various devices of people's lives such as laptop, auto sensor light, phone, television, radio, cars, robots, laser, GPS, Aero planes, vehicle, school, street, office...etc. The concerns with PCB manufacturing start from customer order where sometimes no particular order is placed (no requirements). Another PCB company's problem is customer order conflict which leads to a delay of the deliverable date; thus, production planning is required. In addition, the assembly line and production process time are also considered part of the PCB Company's problems. One of the problems that causes delay is when there are several stations; each station has the same worker placing different components on the PCB. For an electronic company to maintain in the market with other competitive companies, the company must persist in enhancing their manufacturing process to obtain high quality products with fewer budgets. In addition, in order to have an accurate optimization plan, the time of the process on the real assembly line of the manufacturing needs to be known for each machine on the line. In this paper, we will present a study of the assembly line of printed circuit board for one of the PCB manufacturing companies and determine the bottleneck of which machine takes more time and then obtain a solution that could be applied for any other PCB assembly line.

<sup>•</sup> Kamal Alzameli DEMS student-Doctor of Engineering in Manufacturing Systems, Design and Release multimedia system engineer, Research and vehicle technology, Ford Motor Company.

<sup>•</sup> Dr. Daw R. Alwerfalli Professor, Lawrence Technological University, A. Leon Linton Department of Mechanical Engineering. 21000 West Ten Mile Road, Engineering Building, Southfield, MI 48075

# **2 LITERATURE OVERVIEW**

## 2.1 Scheduling Methodology

The main emphasis of most researches has been on the optimization of a single placement machine. Yongzhong, Kim, and Maimon [1, 21, 23] all had similar problems regarding scheduling PCBs. Yongzhong shared a similar objective with Kim in which both [1, 21] had a goal of reducing the total tardiness of jobs , whereas Maimon's main goal was to schedule PCBs on a single machine using a GA approach and reduce the total number of component addresses switches. a manufacturing Yongzhong scheduling problem for PCB with multiple lines. The main investigated problem is to schedule a set of PCB assembly jobs with different ready times and due dates on multiline assembly, with the objective of reducing makespan and the "total weighted tardiness of jobs". The scheduling problem for PCB assembly with multiple assembly lines was investigated by Yongzhong. A complete mathematical model (mixed integer linear programming) for the problem was established and a specific algorithm (GA) was proposed. The objective of the scheduling problem of reducing the total weighted tardiness and the makespan is mathematically modeled by:

min  $(\sum_{i \in N} P_i L_i + qCmax)$

(1)

i, indices of jobs N set of all jobs excluding the dummy jobs  $L_i$  tardiness (in time) of job i q weight for minimizing the makespan of all jobs  $P_i$  weight for minimizing tardiness of job i Cmax the max completion time of jobs,

Constraints between jobs and sequence-dependent setup times are considered in the model to ensure a realistic schedule. Additionally, test instances were generated and solved using a commercial LP solver CPLEX 10.2 in order to verify the model. This mathematical model was able to find optimal solutions to small problem instances; however, optimal solutions cannot be achieved for large instances. To solve real-world multiline scheduling problems for PCB, Yongzhong proposes the genetic algorithm (GA). GA with a new replacement strategy was used to solve different types of optimization problems in PCB assembly. Yongzhong conducted experimental tests and a case study to ensure the usefulness and effectiveness of the method. Effective scheduling results were found when comparing the schedule obtained by the GA with that obtained by the company scheduling staff. The proposed GA method obtained a better schedule with a makespan of 8.88% shorter than that obtained by the company scheduling staff. Consequently, reduced makespan results in higher production efficiency for PCB manufacturing. Similarly, Kim and his teamwork examined a scheduling problem in a factory manufacturing PCBs. Since the PCB assembly process in this factory manufactures more than one machine and independent jobs in the same order, it is considered as flowshop. The main goal in this flowshop is to meet the particular assembly schedule assigned for the final products such as reducing "the total tardiness of jobs with due dates given by the input schedule of the assembly line for the final products". [21]

This flowshop differs from the usual flowshops in which it contains two distinct characteristics. First, jobs contain sequence dependent setup times and second, each job is made of a lot (batch) of the same PCBs. There is an interval between start times of sequential processes of a job in which it makes it possible to start a job on the next machine before the previous machine has even been completed. In this flowshop scheduling problem, the main objective is to reduce the "mean tardiness". For this purpose, Kim and his teamwork proposed some "heuristics including taboo search (TS) and simulated annealing (SA) methods". The two methods taboo search (TS) and simulated annealing (SA) were compared after a set of tests done to find the most applicable values for parameters required in the two algorithms. The search heuristics for a flowshop scheduling problem in a PCB assembly process proposed by Kim and his teamwork were tested and results showed that the simulated annealing (SA) method outperformed taboo search algorithms.

Moreover, Maimon focused on the decision made regarding the process of automatic insertion machine before the production. They focused on developing a method for scheduling a series of PCBs on a single machine being able to automatically interchange electrical component "where the time needed for component switching is significant relative to the PCB assembly time." The problem they addressed is determining the set of components that must be "retaped and rolled" on the master spool prior to the process of PCB. Common components left on the machine may decrease component loading when the total number of various "components required to process all N PCBs is greater than the capacity of the spool." More than one component switches must take place if the necessary components are not on the master spool; the component switches must take place prior to the PCB process. The main problem addressed consists of locating the sequence to scheduling the PCBs on the axial insertion machine and the component placement on the spool prior to PCB process. Maimon's main goal is to schedule PCBs on a single machine using a genetic algorithm approach and reduce the total number of component switches. They came up with a genetic algorithm method to the component switching problem. "A heuristic solution based on a travelling salesman formulation" was used to assess the performance of GA. On the other hand, Mohd [2] addressed Assembly Sequence Planning (ASP) and Assembly Line Balancing

Sequence Planning (ASP) and Assembly Line Balancing (ALB) problems among the assembly optimization, which are considered as NP-hard problems. Soft computing approaches were used to solve Assembly Sequence Planning (ASP) and Assembly Line Balancing (ALB) problems. In the article, soft computing method is defined as *"an approach that is characterized by the use of inexact solutions to computationally hard tasks for which an exact*

*solution cannot be derived in polynomial time.*" Mohd surveyed the past 10 years of research that worked on the ASP and ALB optimization using soft approaches.

The main objectives of optimizing ASP mentioned by Mohd are to reduce the number of assembly direction changes, reduce the number of tool changes, and reduce assembly type change. There are multiple-objective optimization techniques used in other ASP research. The objective of reducing assembly tool travel distance is correlated with PCB, which included robotic pick and place arm. On the other hand, ALB's most frequent optimization objective is to maximize workload smoothness which is measure by calculating workload deviation:

$$\frac{\sum_{i=1}^{n} Ct - Pt_i}{m}$$

(2)

n: number of component Ct: cycle time Pt: processing time M: number of workstation

According to Mohd's review, the most frequent soft computing methods used to solve ASP and ALB problems are Genetic Algorithm (GA), Ant Colony Optimization (ACO), and Particle Swarm Optimization (PSO). GA was preferred by researches in solving ASP and ALB problems because it can deal with more complex and various constraints problems. In short, Mohd concluded that research trends indicate that ASP and ALP are progressing to a more complicated problem due to numerous papers working on multi-objective optimization; therefore, researchers are exploring and developing algorithm that manages such complicated problems.

However, Vujosevic and Bhatnagar [33, 12] shared related objectives and one of the objectives they both seem to focus on was decreasing the lead of the machine operation. Vujosevic and team member prepared a study for the lean kitting in year 2012. Kitting is gathering all parts wanted for the assembly line of printed circuit board, in other words, it is the initial phase for PCB assembly line. Vujosevic tried to determine and eliminate the waste for each station of the assembly line by reducing the WIP, lead time, part damage and then maximize the machine operation by preparing enough parts for each station; as result, the machine would not stop due to the shortage of stock. Downtime, lead times, and manpower gets greater when kitting problem appears. Vujosevic used Arena simulation to simulate the cycle time and processing time for license plate and manpower with two proposed solution and then many recommendation for electronics assembly plants. Arena is a "one-step, graphical modeling and animation system that is based on concepts from object-oriented programming and hierarchical modeling" [24]. The Arena product family is a set of products for many business requirements in modeling, simulation, and optimization. The suite includes Arena Business, Standard, and Professional Editions "for mapping

processes and simulation discrete and continuous systems" [25]. Bhatnagar and his team studied the role of order release and product mix coordination in a complex PCB manufacturing line using batch processors. They improved a planning methodology for organizing manufacture in a PCB assembly line that includes batch processors. They define the objective of the problem and the management process of a complex PCB manufacturing line located the at Northern Telecom's Fiberworld Division in St. Laurent, Quebec. The goal of their project was to decrease the lead time for manufacturing different products while meeting the monthly demand. The present observed lead time in the plant was about 15 days per PCB and using their procedure, it got reduced to 3 days. The planning methodology developed by Bhatnagar and his team included developing mathematical programming models for determining a framework of batch processors, order release, and daily loading decisions.

The processes of the shop simulated by a GPSS mathematical program model, in which it computes the work-in-process (WIP) levels, lead times, and statistics wanted. The program requires input of a monthly wiring plan which regulates the load of transmission devices in each oven during that month, a daily order release plan which specifies the amount and sequence of different boards, and a daily burn-in plan in which subassemblies are to be loaded in each burn-in oven. The decision of order releases are based on product mix necessities of the batch processors, whereas the loading of the batch processors deals with the variability in the manufacturing line. The process they developed in their work was used as a main tool for coordinating production on the shop floor to reduce lead time and WIP.

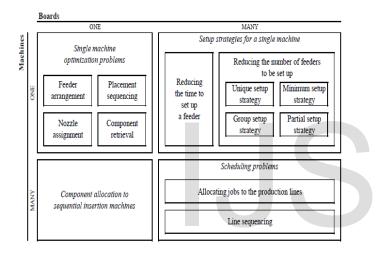

While Vujosevic and Bhatnagar [33, 12] worked on decreasing the lead time, Johnson and Smed [8] focused on solving the optimization problems that occur in PCB assembly. Due to various planning and control problems on PCB assembly, hierarchical decomposition is usually used to solve such problems. Johnson present a hierarchical classification scheme for the optimization problems that occur on PCB assembly. They mainly focused on tactical and operational level problems in PCB. Tactical level "determines the allocation patterns of the system production capacity to various products so that external demands are satisfied". Operational level "coordinates the shop floor production activities so that the higher level tactical decisions are taken into consideration". [8]

Starting at the top of operation and tactical level on a hierarchal classification is the scheduling problem; this includes how to control the machinery to produce various PCBs. The next hierarchal level is the grouping and line balancing problems. Line balancing aims at balancing the workload of different machines while producing a single PCB; the grouping problem objective is to decrease the operation time by making a common "*feeder set-up*" for various products. The lowest level on the operational level is the single machine optimization problem.

Johnson and Smed classify PCB assembly problems

according to the number of different board types being one or many, and machines being one or many as describe on fig1. The four main problem classes are:

1- One PCB type and one machine (1-1): contains single machine optimization problems, its aim is to reduce printing time of the machine. [8, 37]

2- Multiple PCB types and one machine (M-1): contains setup strategies for single machine. "*There are two approaches to reduce set up times* (1) *reduce the time to set up a feeder, and* (2) *reduce the number of feeders to be set up*". [8, 37]

3- One PCB type and multiple machines (1-M): focuses on component allocation to sequential insertion machines. The aim is to balance the workload of the machines in the same line. [8, 37]

4- Multiple PCB types and multiple machines (M-M) or scheduling problems: aims on allocating jobs to lines and line sequencing. [8, 37]

Since there are varieties of problems in PCB assembly such as component insertion, hierarchal decomposition is the solution to such problem. The hierarchal classification scheme helps optimize PCB assemble line in which it makes it easier to identify the problem and find a proper tactic to solving the problem. As stated by Johnson and Smed the classification scheme provides support for practical issues. Like Johnson, Crama and his teamwork [8, 64] surveyed production-planning problems in PCB assembly. Production planning decisions usually hierarchically decomposed into different optimization subproblems including long-term issues known as strategic, medium term issues known as tactical, and short-term issues known as operational. Crama and his teamwork study the long term (strategic) decisions provided in addition to focusing on the medium and short term decisions. The production planning process included eight of subproblem in their study. In their survey, Crama and his teamwork studied single machine, single board type problems; single machine, multiple board type problems; then focus on multiple machines, multiple products problems. They have also reviewed the literature on process planning for the optimization of PCB assembly.

Moreover, Miamon, Dar-El, and Carmon [9] examine two scheduling methods that decrease the set-up times on a PCB assembly line, since PCB assembly line configuration is known by the very long set-up times. The main focus of the authors is to reduce production costs by effective scheduling methods. They examine two scheduling methods that take advantage of component commonality among PCB types resulting in substantial reduction set-up times, the Grouped Set-up (GSU) method and the Sequence-Dependent Scheduling (SDS) method. The (GSU) and (SDS) methods are "compared in terms of three performance measure: line throughput, average work-in-process (WIP) inventory level, and implementation complexity"

The GSU method's focus is that on every different machine the sets of PCBs are produces in two phases, first being the common set-up and assembly and second is the residual set-up and assembly *"the common components are set-up on the machine only once for the whole group, and are assembled onto their respective PCBs"*. The SDS method's main goal is to reduce the number of component changes required during the sequence, maintaining a low WIP level.

The two scheduling method introduced in the paper outperform the traditional scheduling method in terms of reduced set-up times and higher throughput. The GSU scheduling method outperforms the SDS in terms of throughput whereas the SDS method outperforms GSU in terms of the average WIP level. On selecting the most appropriate method to use for a specific production environment depend on some examinations as mentioned by the authors in the paper. The traditional method should be used when the number of common component is small, the GSU should be chosen when the PCB assembly line is a bottleneck operation in the assembly, the SDS method is simple in operation and has a reduced WIP level compared to that of the GSU method. The set-up saving schemes for PCBs examined by Maimon are the most effective scheduling method in terms of reducing the set-up time and in terms of reducing production costs.

There are various problems in planning and scheduling PCB assembly. One of the major problem that encounter PCBs is the distribution of "component feeders to locations in the component magazine at each placement machine and sequencing the placement operations for each machine and PCB type." [16] Grunow and his teamwork present a methodology for scheduling the operations of collect-and-place machines. They study a case where only a single type of PCB is assembled in a high volume. They set up a methodology to calibrate the machine operation to increase the productivity of the whole assembly line and this is done by scheduling the operations for collect-and-place machines in PCB assembly. Grunow and his teamwork's main goal are to decrease the cycle time for the assembly of a particular board. They decided on four main problems to

International Journal of Scientific & Engineering Research, Volume 7, Issue 6, June-2016 ISSN 2229-5518

be solved which are:

1) The assignment of a single component feeder to locations in the magazine.

2) The allocation of placement operations to different tours of the placement head.

3) The sequence of the placement operations in each tour, and last, the arrangement and direction of these tours in a general tour.

Grunow and his teamwork propose a three stage "heuristic solutions" to the problems mentioned above. In the first stage, the problem of assigning single component feeders to position in the magazine is solved by allocating the feeders to positions in the magazine of the machine via a "greedy algorithm adapted from Grunow." In the second stage, the problems of placement operation to the different tours of the placement head, positioning placement operations in each individual tour, and the order and direction of these tours as a general tour are solved. All three problems are presented as vehicle routing problem and are solved by determining the component placement arrangement which is based on the allocation of component feeders to magazine positions. In the third and last stage, "local search principles are applied in order to improve the feeder assignment and the component placement sequence obtained." While Grunow achieved his goal of decrease the cycle time for the assembly of a particular board using heuristic solutions, Guo [17] achieved it by reducing the amount of turns and the amount of pickups. Placement machines establish the bottleneck of a PCB assembly line. Guo and his teamwork focus on certain type of placement machine which is called the beam-type placement machine. This type of machine has "a pickup placement beam at the gantry under which there are several heads that can hold a certain nozzle type (NT) at a *time."* The beam type machine can pick up numerous components from feeders to be placed on the PCB instantaneously; a single component can be picked up by one or multiple nozzle types. The main target of the PCB assembly scheduling for a placement machine is to decrease the cycle time "based on the average machine operation time instead of the travelling distance" and as a result increase the machines output. The reduced cycle time is obtained by reducing the amount of turns and the amount of pickups.

Moreover, there are four main problems to PCB assembly scheduling with an alternate nozzle types for one component which are solved in their paper. The four optimization problems are the "nozzle assignment problem, the head allocation problem, the component type (CT) grouping problem and the pickup clustering problem which are optimized successively and iteratively." The nozzle assignment problem is considered an integer programming problem and is solved by a proposed GA. The head allocation problem is solved to reduce the amount of turns. The component type problem and the pickup clustering problem are both applied and solved together to reduce the number of pickups. The CT grouping problem is solved by planning a greedy heuristic" to form original pickups which are categorized as non-SP6 and SP6 pickups (simultaneously picking up to 6 components). The pickup clustering problem is solved by a modified agglomerative hierarchical clustering in which it forms the ladder from the single elements by gradually integrating clusters. The methods proposed to solve the CT grouping problem and the modified agglomerative hierarchical clustering for pickup grouping problem seemed to perform better than the "brute force method and lower bounds of the cycle times."

Dessouky [18] and his teamwork came up with a method for the design and scheduling of flexible assembly lines for printed circuit boards. The objective of the design and scheduling approach is to get the most out of the throughput of the system while retaining the "work-inprocess (WIP) inventory level to a minimum without increasing the capacity of the assembly facility." This design is based on the concept that it is simpler to regulate and schedule flow lines than "general production lines because for a flow line the scheduling problem is reduced to a sequencing problem. " The main idea of this method is to diminish the setup of machines to a single flow line of workstations.

The method is made up of two phases. In the first phase, identical and nonidentical machines are gathered into workstations in which they're visited by each product in the same order; consequently, the processing is converted into a flow line arrangement. In the second stage, since the processing is now converted into flow line configuration, the products on the workstations are scheduled. Dessouky and his teamwork used the assembly line balancing problem to cluster identical and nonidentical machines into workstations; the machines are dispersed evenly through all workstations in which the output is increased and the WIP inventory level is reduced. "The throughput of the system is defined to be the total daily output rate of all boards." Dessouky and his teamwork's approach for the design and scheduling of flexible assembly lines for PCBs worked well in maximizing the throughput of the system, even flow line configuration, and reduced WIP inventory level.

Kelbel [40] performed his doctorate study on scheduling in manufacturing systems, and he mainly focused on "*just-intime inventory strategy*" to explain scheduling issues in the early stage and the cost that come after this stage. Also, Kelbel studied re-optimizing the component allocation in surface mount technology assembly system, which is the most common issue arising among the SMT; it is how to dispense the components to several machines on the assembly line. Of course, one of the important issues that he looks at it is the setup. The three items that are performed in the this study are grouping issues at maximum level, assignment of components at last level, and sequencing of placements components.

Printed circuit board assembly (PCBA) process plan and scheduling (PCBAPPS) are interrelated. In process planning, assembly processes are defined by "component allocation and assembly machines for each operation are determined by PCB assignment" [19] In addition, process planning delivers a complete regulation of process for scheduling. In scheduling, the assembly order and startand-end of every PCBA process on consistent machine is determined. The major objective of process planning is to attain the least cost and achieve the assembly requirements of every PCB. In scheduling, the main goal is to complete all PCBA assignments for "machine resources to meet time and machine constraints and then, not all the PCBA process plans might be schedulable according to the time and resource availability" [19] Du and his teamwork developed an integrated method for PCBAPPS which is considered a difficult combinatorial optimization problem. They studied the integration of PCB assembly process planning and scheduling to develop product quality, reduce assembly time, and reduce production cost. Based on the polychromatic sets (PS), Du and his teamwork developed an integrated method of PCBAPPS based on logical and unified contour matrix. To optimize the integration problem of PCBAPPS, a hybrid generic algorithm (HGA) has been developed along with the PS model. The PCBAPPS optimization problem solves the problems of PCB assignment, component allocation, and PCB sequence by balancing the workload, decreasing the delay time, and reducing the makespan of PCBA assignment.

Sabouni [62] also used an integrated method to solve scheduling problems. He performed a study for carryover sequence-dependent group scheduling with the integration of internal and external setup times to discourse a group scheduling problem. His objective was to minimize the group family by carryover setup machine in different projects; the objective was to eliminate complexity of the kitting. Mathematical model and genetic algorithm (GA) was developed for this investigation.

#### 2.2 Placement of Components

Designing a PCB has a set of components that needs to be assembled. This assembly task involves placing PCB components at the selected location on a PCB board, fixing PCB components, and then testing the PCB after the assembly to make sure it's working properly. Placement machines work together to form an assembly line for component placement on a PCB. The use of more than one machine for component placement on a PCB causes a line balancing problem; this affects balancing the workload of all the machines in an assembly line. Khoo [7] described the application of a new artificial intelligence technique, the immune algorithm (IA). "Immune Algorithms (IAs) are search algorithms based on the mechanics of immune systems." Khoo described the application of IA to PCB component placement along with line balancing of PCB assembly line. His main objective was to reduce the cycle time of a PCB assembly line using the IA technique. Two case studies were done by Khoo and Alisantos to validate the IA engine developed in their work. Case study 1 is a comparative process used to validate the IA engine. In case study 1, the immune algorithm (IA) out-performed GAs in terms of both distance traveled and time taken. Using IAs in Case study 1 showed a noteworthy development of 22.6% in distance and 21.3% in time in a PCB assembly line.

Case study 2 is used to validate line balancing capability. In case study 2, an assembly line balancing procedure is combined into the IA engine and modifying the objective

function. IA parameters were chosen and based on those parameters; the IA engine was able to bring out the best balanced cycle time to be assigned to the five machines used. "*The assembly line balancing efficiency was computed using EQ.92*) to be 99.3%."[7] Line balancing of PCB and sequencing the component placement using the immune algorithm (IA) engine was a successful approach.

PCBs are factory-made, in today's electronic industry, in automated assembly line in which high-speed placement machines position components on the boards. Salonen [10] and his team examined the single machine setup-up problem (M-1) (M-1: Multiple PCB types and one machine) in a high-mix low-volume environment. They combined a job grouping problem and a minimum feeder setup problem n PCB assembly for a single machine setup. They expressed this combined problem as Integer Programming model in which their main objective was to reduce "the weighted sum of the number of setup occasions and the total number of component feeder changes".

While Khoo [] used the immune algorithm (IA) to reduce the cycle time of a PCB assembly line, Salonen [10] used a different algorithm based on different objective. Based on both grouping and minimum setup strategies, Salonen and his team presented new hybrid algorithms (GSA) group setup algorithm. They repeated the experiment for each dataset 100 times using each time different randomly chosen PCBs from a production program of a high-mix low-volume environments. The hybrid algorithm GSA shown to produce the best results overall. The best results for grouping and sequencing PCB assembly jobs with minimum feeder setup can be achieved by a method that uses both of these strategies instantaneously.

Furthermore, selecting the best PCB assembly line system from a set of alternatives can be difficult for PCB manufacturers. Santos [13] and his team focused on the assimilation of different software packages into "a decision support system." The decision support system provides manufacturers of PC assembly line systems with different configuration to its customers. Scheduling an assembly line system is mainly based on the manufacture requirements of the customer. These production requirements include several factors including: "the number of different types of PCBs to produce and the quantities of ach type of PCB to produce" Moreover, the production requirements contain " the materials related factors per board type" which include the kind of substrate, the amount of diverse part types, and the amounts of parts per part type. As stated by Santos and his team, the process of the placement process is the major factor that determines which assembly line system to use; the placement process is the step that takes up more time compared to other production process. Using the software tools combined into a decision support system has saved time for assembly line manufacture by proposing replacement assembly line configurations to its customers. Altinkemer [14] and his team studied the surface mount technology (SMT) with a computerized numerical control (CNC) machine retaining a rotary head. Rotary heads are able to pick up more than one component at once.

Altinkemer and his teamwork focused on a CNC with a rotary head that allocates components of similar type at the same time and place them on the PCBs. They concentrated on the optimization of PCB manufacturing by providing integrated models and algorithms that included all sub-problems together as a single problem. The three sub-problems in the manufacturing of PCB are sequencing of component types a PCB, distribution of component types to feeder at every PCB, and pick-and-place placement sequencing.

Altinkemer and his team designed an algorithm that tries to solve the subproblems, component allocation to feeders and the sequencing of placement. In addition, they demonstrated their integrated algorithm having an error guarantee of  $\varepsilon$  if the error gap of every vehicle routing problem is  $\varepsilon$ ; otherwise, the error gap is regulated by the vehicle routing problem that has the biggest error gap. They presented a solution with a  $\varepsilon$  -error gap for PCBs problem; "an error gap less than or equal to the maximum error gap of the vehicle routing problem costs." Their integrated algorithm can be used to achieve the best PCB solution when the optimal routing problem costs are identified. The surface mount technology with a CNC machine using a rotary head provides optimization methods and algorithms applied in PCB machines.

Similar to Altinkemer and the use of rotary heads that pick up more than one component at once, Li [15] and his teamwork study the problem of reducing the PCB assembly time using a multi-head surface mounting machine. The multi-head surface mounting machine helps reduce time in which it picks or place several components at the same time in one pick-and-place process. The total PCB assembly time is determined on two optimization problems in a surface mounting machine which are feeder assignment problem and pick-and-place sequencing problem, both are "combinatorial nature and NP-hard." The feeder assignment problem is very important and has a direct effect on the surface mounting machines productivity and thus it is studies by Li and his teamwork.

Li and his teamwork focused on the development of optimal feeder assignment of the multi-head surface mounting machine via genetic algorithms. When a feeder assignment problem is solved optimally, it decreases sum of time of moving slots, "moving from slots to PCB and moving from PCB to slot for placement heads griping components". This is done after setting the pick-and-place sequence in advance. The genetic algorithm presented by them is used with "specific integer coding, uniform order crossover and exchanging mutation operators." Li and his teamwork did an experiment to prove the optimization method using the genetic algorithm. The optimization method is considered as a module and thus the GA module is encoded through Visual C++6.0 using uniform order crossover and exchanging mutation.

A solution of reducing the production time of the feeder assignment problem with surface mounting machine was obtained using GA. The optimization of the feeder assignment problem by the specific genetic algorithm used performed better compared to typical methods.

Like Altinkemer, Li and Wiklund [14, 15, 38] also focused on multi-head placement machine. They studied optimization of the feeder assignment for PCB assembly machines to minimize the production time via placement and setup optimization. Wiklund categorized placement machines into five following modules where he focuses on Multi- Head Placement Machine study only.

1- Dual Delivery Placement Machine

2- Multi-Station Placement Machine

3- Turret Style Placement Machine

4- Multi- Head Placement Machine

5- Sequential Pick-and-Place Machine

Similarly, Shrivastava [39] performed his study for the placement machine and how to minimize the "distance travelled", and then he compared his results to other researchers that used different method of algorithm for the same type of problem. He used a hybrid Artificial Immune System (AIS) -technique of grouping- procedure to explain serial pick and place (PAP) problem in placement machine. The component placement machine is a vital part of manufacturing equipment on a surface mount assembly line. The component placement method is usually the bottleneck and thus, developing the processing times of the placement process guarantees an improved work flow and benefits the output in which it optimizes the output. To optimize the process, the machine's cycle has to be reduced. Hardas [20] and his teamwork focus on the improvement of a genetic algorithm for component placement sequence optimization in PCB assembly. They explain the progress and the assessment of an application that determines genetic algorithms usage in order to solve a component placement-sequencing problem for PCB assembly. Since numerous component are placed on a single PCB, developing an application that defines an "optimal or nearoptimal placement sequence" is helpful in which it reduces the overall cycle times of the assembly in addition to reducing assembly costs. An application was developed to assess how effective is the usage of genetic algorithms in solving the component placement sequencing problem. The main goal of Hardas and his teamwork's study is to enhance component placement sequencing by reducing the "distance" traveled by the head of a single-headed placement machine." They used an experiment to define the top "representation and crossover type, crossover rate, and mutation rate to use in solving the component sequencing problem for a PCB consisting of 10 components placed on a single-headed placement machine". Three different representations along with six crossover types were assessed at three different mutation rates and at eleven crossover rates. Mood's media test was used to compare the three response variables. Based on their study, the most important parameters in the GA design was the grouping of representation and crossover type along with mutation rate; the sequencing solution made a 57% reduction in head travel time which is an important factor in the board assembly cycle time. These parameters do not only affect the quality of the solution gained but also the speed at which "a near-optimal solution" is gained.

On the other hand, Ayob [47, 61] performed his Ph.D. study on optimization of SMT device placement machine in printed circuit board assembly. His main objective was to improve the pick-and-place process via producing operative scheduling method that can enhance the throughput, as well as improve "the robot motion control, nozzle selection and feeder setup"

Ayob completed an investigation about a survey of surface mount device placement machine optimization. This survey expressed the features of several machine technologies and organizes them into five classes based on their requirements and working procedures.

While Ayoub performed his research on optimization of SMT device placement machine in printed circuit board assembly, Quintana [51] performed a research to enhance productivity in manual electronics assembly and inspection through illumination design. He used three factor full factorial experiments to evaluate two variables, the assembly time and process revenue.

# 2.3 Design printed circuit boards

The assembly process contains a number of machines for placing all the required electronics components on a bare PCB. The use of surface mount technology (SMT) has made the manufacturing of electronic products much faster and less expensive by using *"high-speed manufacturing processes and miniaturized components."* [6] In the article, Emet considers balancing the workload in PCB assembly. Various researches have been done on balancing PCB assembly and numerous methods were used. Emet main's goal is to allocate the assembly processes of a single PCB type to different machines resulting in increase in the throughput of the line (the number of finished PCBs per time unit).

Supposedly, the total production time is a linear function of the number insertions made by a machine; this is the simplest model used in line balancing. To solve the line balancing problem, Emet finds a fast method for estimating the single machine production times. He used a mixed integer linear programming (MILP) model using the CPLEX-software. Extending on to the model, he considers the usage of the feeder modules and precedence relations between the placement operations.

Emet performed an experiment with the line balancing formulations; he used standard optimization tools to solve the balancing problem. In conclusion, line balancing problem was solved using the CPLEX-software in it which able to solve MILP formulations. Three different placement machines with up to 150 different component types and problems containing up 400 to 6,000 component placements could be solved using the CPLEX-software on a normal PC. As system design is becoming more complex developing cost are increasing and thus, estimating design time is becoming difficult. Design effort metric is beneficial in helping reducing design costs. Bazeghi [6] introduces µPCB Complexity which is a "*methodology to measure and estimate PCB design effort.*" Bazeghi and his teamwork analyze and propose various statistics to estimate design time for

developing PCBs. Using the μPCB complexity methodology, Bazeghi and his teamwork investigated and measured contributions of the different elements in the design such as "area, component count, pin count, and device types and sizes for many PCBs." They also used a non-linear statistical regression to obtain a good design effort metric. In his paper, Bazeghi presented a design effort metric that is interrelated with design effort for PCB layout. Bazeghi and his teamwork used µPCB complexity to evaluate series of design effort metric for twelve PCB design from two separate companies. They analyzed electronic devices such as computers and obtain data from their PCBs; the layout time for these PCBs was obtained for the purpose of the analysis. They presented their design effort model as the "aggregate of a set of statistics."

Design Effort=

$$\frac{1}{p} \times \sum_{k=1}^{n} (w_k \times s_k)$$

(3)

P: the aggregate of the statics in inversely proportional to the productivity of a specific design team.

W: constant for each set of statistics.

S: set of statistics

They used a non-linear regression model in addition to the standard deviation of the error  $(\sigma)$  to compute the confidence interval. They used simple statistics such as number of components and pin count on a PCB design to compare the accuracy of  $(\sigma)$  and the 90% confidence interval. Results showed that µPCBComplexity methodology works better in estimating design time for system circuits. Their study showed that with 90% confidence, pins has a (0.47, 2.09) confidence interval which means the typical design time error is half with 90% confidence whereas using µPCB Complexity metric, better results were achieved. The confidence interval for a 90% confidence is (0.58, 1.72) which means fewer than 40% estimation error is made with 90% confidence. [66, 67]

While Bazeghi [6] introduced  $\mu$ PCB Complexity methodology to measure and estimate PCB design effort, Chincholkar [46] performed his Ph.D. study on design for production to analyze how the product development will influence the manufacturing system performance. Therefore, this study is a relationship between the product design and manufacturing system performance and the main aspects for these relations are the WIP and cycle time. Chincholkar provided deep study on the design side for each passive device, the single passive component like capacitor, inductor or resistor in PCB SMT; as well as studying the material of these components and the layer of the PCB.

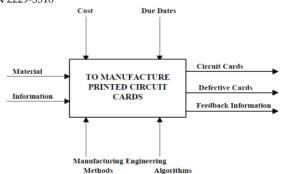

Focusing on the same subject of designing a PCB, Nakagawa [60] performed a study to optimize the design of printed circuit board to reduce deformation in reflow process by a global optimization method. He focused on studying the circuit layer and the thickness and how it is impacted by the reflow process; then the relationship between stress and strain of the PCB. *"The relationship*  International Journal of Scientific & Engineering Research, Volume 7, Issue 6, June-2016 ISSN 2229-5518

between stress and strain of the PCB is modeled by using the laminated composite theory in order to estimate deformation of the PCB. The area ratios of copper in the circuit layers and the ratios of thickness increase in the insulator layers are determined to decrease the PCB deformation" [60]

General guidelines for deign electronic components (printed circuit board) is explained in Halbo [59] book to provide better quality and meet costumer expectation. All of the following items have been considered into these guidelines: specification, performance, reliability, deign for the manufacturing and testability, design for essay to fix, and essay to package. Dimensions of solder are another important factor that was studied which shows minimizing solder faults and strength of the solder joints. Another important aspect mentioned in this book is the thermal deign to show the assessment of the temperature during different phases. "An important reason for doing thermal design is the fact that increasing operating temperature results in shorter expected operating life. Typically for electronic products, a 10°C temperature increase reduces the life length by 50%".

#### 2.4 PCB Inspection

Very precise PCB inspection has been requested by many electronics manufacturers for a perfect quality in the PCB assembly process. Detecting defects in PCBs through "conventional rule-based inspection algorithms" is no longer sufficient. Through Chia-Te Liao [4] study, a flexible PCB inspection system based on statistical learning strategies is developed. As stated in the article, template-matching technique proposed by Akiyrnai was the first developed PCB inspection algorithm. Later on, various PCB inspection methods were developed by different people. PCB defects such as open, short, pinhole, under- etch, or mouse bite is cause by various reasons including dirt on board or incorrect electrolysis timing. Chia-Te Liao presented an experiment to demonstrate the effectiveness of the automated learning-based PCB inspection system. Two steps were used to inspect PCB for defects. The first step is image alignment in which the image attained by the camera is aligned to the stored reference image to determine the position of defects; this is done by using the partial Hausdorff distance. The second step is image diagnosis and is performed by identifying two kinds of defects in two different ways, 1) the defects that appear as "patterns," and 2) the cosmetic defects without regular appearance. The experiment indicated that the learning -based AOI system provides reliable and flexible solutions for PCB inspection. The system is able to classify new defects simply by adding defective samples into the database. In addition, the system develops a "probabilistic solution" to detect defective regions and measure the defectiveness amount. Inspecting PCB defects using the AOI system is beneficial and will help detect PCB defects.

On the other hand, Hsiang [27] performed his study on process capability for the stencil printing in printed circuit board assembly. Hsiang emphasized his research on stencil of solder paste into PCB as opposed to Chia-Te Liao development of flexible PCB inspection system based on statistical learning strategies. Since this area is one of the critical process phases in the SMT. The evaluation techniques he used was hypothesis tests and cause and effect diagram to identify the root case; then he used SPC (statistical process control) and process capability (Cp/Cpk) to analyze if the solder paste height can be used. Hsiang used three types of the inspections; solder paste measurement, automatic object Inspection (AOI) and automatic test electronics; and then touch up which is manual rework station.

Test PCB design is important to define the purpose of the test board and reliability problems and concerns. Smetana and his teamwork [73] conducted a study on the solder joint reliability of high density packages using lead-free solder. They addressed the design, materials and process for lead-free assembly of high-density packages. They wanted to assess the solder joint reliability of lead-free (Sn3.8AgCu) solder joints related to eutectic solder (Sn37pb) joints under thermal cycling. In addition, determine differences and impact of the reliability of the same components. As they conducted the study, the components studied such as the surface mount technology package using lead-free solder pastes recognized changes virtual to assembly in "reflow profiling, voiding, wetting, and transition to lead-free." They assembled more than 80 boards using SnPb and lead-free materials in addition to production equipment. X-ray inspection of components was performed to detect any defects; this method ca be used for lead-free assemblies with minimum changes to settings.

While Smetana and his teamwork conducted their study on the solder joint reliability of high density packages using lead-free solder, Barthel and Diehl [74] studied the PCB and test fixture design measures in addition to the main assembly process parameters that affect test probe contact. They investigated the importance of optimizing test probe contact for no-clean electronic assemblies. A multi-phase method was performed to detect and validate a no-clean solder paste with an "ICT fixture design that would allow for vacuum compression when probing via pads." In the first phase, viable no-clean solder paste was selected. In the second phase, the factors that affect probe contact with solder paste filled vias was assessed; "PCB, text fixture, solder paste type and process parameter factors were addressed" in their study. The paste type was the main factor in attaining test probe contact on solder paste filled vias. The authors tested eight different paste types and only three types had enough probe contact.

#### 2.5 Simulation

Mohamad and Chang [3, 26], have similar objectives of increasing the production line but have used different techniques to determine and solve the problems. Mohamad conducted a simulation study towards productivity improvement for assembly line. His study proposed assembly line improvement focused on a Material Handling Operator (MHO) solution as a process simulation method. The main reason of his study is to upsurge the productivity of the ABC Company in Malaysia by a line balancing technique, in addition to improving the productivity using simulation approach. Mohamad described the productivity of the ABC Company as an unsatisfactory and fails to achieve its target output because each workstation is managed by one workstation operator. He used a line balancing technique (cycle time method) to determine the problems. Due to this technique, the company succeeded in decreasing the "total time required to complete 600 product units per week, from 256.49 hours down to 208.06 hours, and the lead time from 5 days to 7.9 hours down to 4 days 6.8 hours."

In the study, Mohamad focused on Material Handling operator (MHO) using simulation method to improve assembly line. A MHO is assigned to transfer boxed containers from one station in the assembly line to another; thus, workers at each workstation concentrate on their own tasks. Two types of simulation models were designed and implemented to assess the outcome of MHO in the production line. One model was without MHO, which is similar to the existing assembly line, and the other one is with MHO in which one MHO is responsible for the material handling task of the whole assembly line. Results showed the process time and the production performance of W-MHO model was better than that of the W/O-MHO model in a simulated evaluation as stated by Mohamad's study. Chang used simulation for PCB assembly plant to improve the production line. Chang and his teamwork's main objective was reducing the manufacturing cycle time and reducing work-In-process to increase the total output. Chang focused on simulation with data collection and building in addition to validation model then improve it on the factory floor. He collected two month data that are relevant to his simulation which is process cycle times, product releasing pattern, equipment breakdown and equipment setup; also, other relevant data were collected like MTBF and MTTR and machine cleaning. Buffer size in front of each station was valued to limit the WIP. After the model is built and verified, the expected results was to reduce the WIP cost by half million Singapore Dollars and reducing the cycle time by 5 days, then increase the output by 70k as total capacity.

Dengiz [28] used simulation optimization techniques to determine a problem condition on printed circuit board manufacturing process. He used Taguchi methodology integrated with simulation model to reduce the cost and timing. Dengiz chose seven factors with levels by using Taguchi method and for simulation, he used five replications on the model for each one of the seven experiments; it showed that experiment is efficient within 5% sensitivity. As a result, Dengiz got 47% reducing cost.

A tutorial on simulation optimization performed by Azadivar [29] emphasized on why simulation is needed and what problems could be solved, as well as he used the technique that response to "what if" and "how if" which measures the performance and seeking for improvement respectively. "Using simulation as an optimization tool for complex systems presents several challenges. Some of these challenges are those involved in optimization of any complex and highly nonlinear function. Others are more specifically related to the special nature of the simulation modeling." One of the four approaches to solve problems Azadivar used was response surface methods (RSM), it is a technique of correcting a sequences of regression model outcome of the simulation model and optimizing the regression functions as an outcome of that.

In the manufacturing process of hard disk drive, the final assembly process is an important section of the process. It is the last stage of the HDD production process in which the "head disk assembly and main printed circuit board are being mounted together, media written with the firmware code, going through a series of functional test before packing for shipment." Ali and Souza [30] study the hard disk drive final assembly process using an HDD template; the HDD template is intended for modeling and simulation of HDD final assembly manufacturing using Arena. To develop a real-life model, Ali and Souza study the internal and external dynamics when "designing the simulation template in Arena for HDD assembly system." The HDD template's main goal is make to the simulation model more realistic for the "internal supply chain in the electronics manufacturing." Moreover, the HDD template is very helpful in improving the systems performance. Any unexpected machine dynamic behavior can be prevented by examining through the intelligent based dynamic machine knowledge. This machine knowledge is able take over dynamic based activities with fuzzy dynamic. All in all, the study conducted by Ali and Souza demonstrates how modeling and simulation tools can be used and how they can be combined to execute "highly automated systems for industrial process and deal with flexible products".

Yilmaz [31] studied the simulation of mixed-model PCB assembly lines with group setup and bypass conveyors. The main objective is balancing the workload on the first stage where component and placement operations for every PCB given to the machines in the assembly line. Then it will go to the next stage where setup is performed as family for similar components. A repeated mixed model production schedule was prepared as final stage. Yilmaz examined two different material flow arrangements "Two alternative material flow systems are investigated: a serial conveyor which directly links one machine to the other and a flexible one that allows to bypass downstream machines in the line." Mixedmodel line does not work with PCB because of the major change needed for screen printer used to put on solder paste onto board. However, lately there are two developments to use mixed-model mode, one of them is the new "lead-free" solder paste and the second one creates more improvement and flexible material control equipment.

Kallio, Martin, and Gebus [32, 35, 22] studied discrete-event simulation from different perspectives and with different objectives. Kallio studied the process time of flexible surface mount placement machines and discrete-event simulation which are used to predict components

placement timing. The only part that move in X and Y directions is the placement head which holds one or more spindle so it can clamps the nozzle for picking component and then place it on the correct location on the circuit board. "There are two different designs for managing the nozzles. In the first one, the nozzles are fixed and can be changed only at product changeover occasions. These machines are often called collect-and-place machines and they aim at higher placement speed. In the second design the nozzles can be changed in-fly during the operation of the machine"

Kallio used observation technique (camera or laser) to check each component position to make sure each one of them is placed on the right location then adjust placement machine if necessary. Also, the tape feeder, tray feeder, nozzles and nozzle magazine are considered in his simulation study.

On the other hand, Martin studied how the discrete event simulation can be used to optimize the electronics assembly line and tried to avoid the worker experience and rely on the facts of the study. "Discrete-event models: A model is called discrete when changes between states happen only at specific times and in a discontinuous way. An event is what causes the change in state of the system. Attributes can usually only have a certain number of values, and states are countable. Resources affectation problems are a typical use for this kind of model". Of course he needs to match whatever results obtained and what workers are saying and compare these two. This study can be done from understanding the environment of the manufacturing floor and facilities. Martin developed a model of current assembly line and identified the issue and bottleneck, then tested different situations for enhancement and implemented any necessary actions for that manufacturing company. Martin used the simulation on other research because the simulation is cheaper and validation can be done without interrupting the real assembly line system. Arena software was selected for this study.

Like Martin and Gebus [35, 22] and his teamwork focused on Discrete-Event simulation and how it can be used in production optimization of electronic assembly lines; such as printed circuit board assembly lines. Discrete-Event simulation gives an enhanced understanding of the production environment in which it can be used to assess various situations for better production, or maybe provide information for planning a new production system. The model can also be used to examine processes and detect problems such as bottlenecks. Gebus and his teamwork presented a case study in which various scheduling strategies were proposed and results were compared based on planned optimization objectives. The case study presented was about the company PKC Group that produces PCBs, mostly the control cards for the automotive manufacturing. The goal of their study was to make a decision assisting tools "based on intelligent methods adapted to the specific needs of electronics manufacturing" [22] in which two problems were discussed, "defect localization on Printed Circuit Boards and production optimization." Discrete-Event simulation was used as a tool to examine the effect of various

"production parameters on various quality and flexibility indicators." The outcomes showed that the system was effective for new products "even in the ramp-up stage." Gebus and his teamwork had proved that Discrete-Event simulation is a good tool to assess performances of various optimization methods by comparing this result mothed to other methods like GA method.

Discrete-event simulation was also used by Greasley [52]. He accomplished a case study by using discrete event simulation for facility design, the reason for that was to estimate the storage area for the manufacturing facility and determine the work-in-process WIP. The researcher collected the data from the production line and he build the model the in the Arena software.

Simulation modeling of large models usually takes time to develop and authenticate. Johnson [57] and his teamwork studied a modeling decomposition method that is time saving scheme for the modeling process. "Decomposition refers to the process of breaking a large system down into subsystems and modeling each subsystem independently" Model decomposition is time saving because each subsystem can be established by different teams thus, expediting the modeling process. Johnson and his teamwork examined the problem of "decomposing an upstream serial transfer line from a downstream jobshop" like the one found in PCB assembly line. They did an experiment with a model of an actual PCB assembly line system. They built a model of the upstream subsystem to observe "the effect of the setup improvements" They also demonstrated the "downstream manual stations to determine how the output process from the upstream line effect the downstream process"

Nevertheless, Jadhav [44, 63] studied analyzing printed circuit board assembly lines using a custom established PCB assembly template. Jadhav used Arena software to develop the simulation model to capture "unreliable workstations and component parts exhaustion, and pooled operators responsible for manual operations as well as for repair and replenishment of processes". Jadhav's methodology has six steps starting from data collection to configuration modify and returning it; in between is static model of process and a discrete-event simulation developed. Based on the variable data that Jadhav got, three setups has been developed where the first one ignores the machine failure and parts exhaustion; the second setup does not include the parts exhaustion but includes the machine failure; the third setup includes both parts exhaustion but does not include the machine failure. The reconfiguration of the simulation model was based on the discussion with decision manufacturers to select what is the best for the assembly line.

Also, Ilgin [77] and Gupta proposed a simulation optimization method for "joint optimization of the transportation and spare parts inventory policies in a reverse logistics (RL) network designed for End of Life (EOL) television (TV) recycling." The reverse logistics (RL) network includes three centers: a disassembly center, a recycling facility and a spare parts warehouse. EOL TVs and the dissembled EOL

of the RL network to the other. EOL TVs are dissembled by the disassembly facility into PCB; using various PCB types can produce different TV models with similar size. A disassembled PCB is either stored in the spare parts warehouse or in the recycling facility "depending on the inventory level of the particular PCB in spare parts warehouse". A PCB is tested for defects when it's needed by the spare parts warehouse; all other unnecessary and defective PCBs are stored in the recycling facility. A discrete event simulation (DES) model was established in detail via Arena simulation software to demonstrate the reverse logistics (RL) network along with the associated inventory features of its disassembly, transportation and spare parts. Then, Ilgin and Gupta used Arena OptQuest to come up with the greatest number and size of trucks together with the "optimum reorder (s) and order quantity (Q) level for the spare PCBs based on the minimization of total cost which includes inventory holding, PCB recovery, new PCB acquisition, truck amortization an operating costs." The proposed methodology by the authors can greatly reduce operational costs by setting the optimal transportation and inventory level for a RL network in which they have done so by using the Arena OptQuest simulation software.

In contrast to Ilgin and Gupta use of the simulation model, Joseph [78] and Wigglesworth model and analyze new product development in electronic sub-assembly manufacturing. They used simulation model to "support the formation of assembly test and repair process for volume manufacturing." The test, inspection, and repair take up a large portion of the overall production cost in the electronic sub-assembly manufacturing. The production objective was to make sure that the sub-assemblies deliver high quality and consistency with less cost. They focus on joining both product and process engineering. They analyzed a process from a capacity and quality perspective to develop a simulation model that signifies the performance of the subassembly manufacturing process. Fish-bone analysis was used to detect the cause and effect of "faults in sub-assembly manufacturing and to collect the fault data to be used in the simulation model." The IDEF methodology is then used to develop a representational model of the system that describes the sub-assembly manufacturing process accurately.

#### 2.6 Machine setup

Salonen dissertation [37] studied the machine setup issues for low volume products and mix type of printed circuit board assembly manufacturing using multiple PCB type. Hybrid setup issue is the main topic that Salonen focused on his study *"hybrid setup problem that is a combination of the job grouping and minimum setup problems"*. The main objective was to minimize the changeover setup as well as minimize the weighted sum; so, it is a setup optimization research. Salonen and his team research studied two types of setups *"components setup" and "setup occasion."* The first type is focused on replacing one component feeder with additional component, while the other type takes place every time when interruption occurs to the line for one or

new feeder modifications. Salonen used mathematical model in his study, specifically, linear programing (LP) approach and integrated programing (IP) approach models. In the electronics industry, setup time reduction is critical as it increases a factory effective capacity [70, 71]. Setups could take up to 50% of the total operating time in a PCB assembly. Therefore, Trovinger, Bhoja, and Capps [68, 36, 49] study setup time reduction in various ways, each with different approaches and different results. Trovinger and Bohn examine setup time reduction for PCB assembly in the electronic industry combining both Simple "Single Minute Exchange of Dies" (SMED) and IT-based methods. SMED approach, developed by Shigeo Shingo, refers to a setup time reduction from many hours to less than 10 minutes. The authors go beyond the use of SMED method and the situation it was made for. To reduce setup time reduction, Trovinger and Bohn used high speed PCBA process; they applied the SMED approach to setups which consisted of three phases. In the first phase of SMED, the setup tasks are separated as being an external task or an internal task. In the second phase, technical changes are performed such as changes to the design of the machine. In the last phase, all external and internal tasks are "streamlined to make them faster and more (labor) efficient." They combined modern information technology to SMED since SMED put emphasis on process simplification. The modern information technology tools included wireless terminals, barcodes, and a relational database; these tools help with feeder management. The technical development achieved is measured economically by the authors. They estimated that the total line setup time was reduced by more than 80% with saving of \$1.7 million yearly.

Bhoja [36] performed his master's degree at Virginia Polytechnic Institute and state university on the assignment problem in PCB card assembly line; these problems occur in large electronic companies as to allocate the circuit card brands to the right assembly line. Since there are common circuit board among the assembly lines, grouping circuit cards is considered as well. Bhoja determined manufacturing process by process planning based on the information of the product design. There are two issues in process planning for the assembly line that Bhoja considered in his study which are process optimization and setup management.

"Process planning in electronics assembly involves addressing two closely related issues: process optimization and setup management. The primary focus of process optimization is processing time efficiency while setup management refers to the planning decisions regarding the organization and allocation of resources and products in the assembly system" [36]

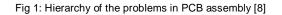

Bhoja described the printed circuit board assembly system as shown in the following illustration Fig2, where he considers the cost and due date of products required by the customer, and then defective PCB and learn a lesson from the feedback information. Bhoja objective was to minimize the "total assembly time" which includes the process time and setup time.

Fig 2. Printed Circuit Board Assembly System [36]

Capps performed a research using Genetic Algorithms to study the setup reduction in PCB assembly. So, his goal is to provide a mix of placement machines via group scheduling. As a result, it will minimize the cost to the manufacturing by the new setup. In addition, mathematical model was developed to determine which solution is more practical compared to GA heuristics.

However, Tóth [45] and his teamwork member performed a study about reconfiguring flexible machine modules of a PCB assembly line; they considered particular factors such as component type that's placed in the printed circuit board. Another factor that's considered is based on the previous factor "components type" where each type of component requires special head and nozzle kind "different component types require different head and nozzle types in their placement operations. Further, as there may be several different head types that can hold different numbers of nozzles, one must consider the nozzle to-head and component-to-nozzle compatibilities." MCLB- machine configuration and line balancing are used in Tóth's study where a single board style is mass-produced via assembly line of re-configurable mechanism components. Minimizing production time is one of the goals that the team studied via configuring the components.

Other research has been done for printed circuit board like quality study. Jokinen [34] and his team member performed a report at the University of Oulu for the qualityforecasting tool (QFT) for electronics manufacturing. The main step that Jokinen did was the database collection; he tested three real quality products compared to QFT system for seven months researching. Since the problem that's facing the team is not linear or unpredictable distributions problem, fuzzy logic was used for this study.

Also, an additional research has been done for printed circuit board. Gebara [43] performed his doctoral dissertation on minimizing cost of variance in the printed circuit board assembly at Lawrence Technological University where his main focus was on developing framework study of cost of variance and develop search tools to optimize cost. Three areas were investigated which are receiving inspection, machine placement, and rework station. The methodology used for this research is the Six

#### Sigma.

Another research, Gebus [41] did a report for defect localization on a PCB with functional testing at University of Oulu, and testing dedicated for the final testing of the PCB. He used linguistic equations and Fuzzy logic for this diagnosis.

Moreover, master thesis studied for decision support system to predict the manufacturing yield of PCB Assembly Lines by Helo [42] at Virginia Polytechnic Institute and State University. A model to predict the developing revenue of printed circuit board was the main investigation in the study with two methods; the first one is "process yield estimation" and the second one is the "board design yield estimation". There are two factors that impact the assembly income on the board design yield, the total components and what kind of components are on the board. The objective was to provide an evaluation for component style error yield which can be accomplished by reducing predicted yields and the actual income.

Furthermore, there is another research that has been done on the machines that produce the PCB like Chang [48] whose doctoral dissertation was about optimizing assembly plans for a robotized printed circuit board assembly center. He focused on three items in his research; the first one is the set of the parameters "a set of parameters was defined for use in analyzing assembly planning problems in robotized PCB assembly centers". The second item is to develop mathematical model for robotic PCB assembly plans optimization, considering the robot movement of X-Y traveling. In addition, the last item was an integrated heuristic method "an integrated heuristic method was developed to obtain near-optimal assembly plans of the robotized PCB assembly center".

On the contrary, Andersson [53] has done another thesis study for process improvement where he performed analysis and Actions for Robust Electronics Production at Haldex Brake Products. PDCA (Plan Do Check Act) cycle methodology is used in this research and the main emphasize is on process stability. Seven phases were used in this methodology starting from finding the measurement then start a "step stone", "new tool in your belt", keep measurement, then round plan so it can implemented in the plan; then note outcome, and finally lean. The aim of this research is to improve the first time pass rate.

Oresjo [55] performed a study for a new test strategy for complex printed circuit board assemblies. The new recommendation for the new strategy is to use the AXIautomatic X-ray inspection instead of manual visual inspection. Arvind [56] performed value stream analysis on a printed circuit board (PCB) production line. The purpose is to analyze the process and improve the timing so the (VSM) value stream mapping is used to check existing production assembly line. VSM is manufacturing tools to make it lean devolvement, so remove any none-added value and determine the added value to keep it.

While Oresjo performed his study on complex PCB assemblies, Yazdani [58] and his teamwork addressed the problem of a single-machine carryover sequence-dependent

group scheduling in a PCB manufacturing. They studied the possibility of processing all components of PCBs by a single machine with the objective of reducing the makespan. Their main focus is to integrate the machine internal setup and kitting operation (which is known as the external setup) in a PCB assembly "in a way that the required setup time for transferring to a new board group is carried over all of the previously scheduled board groups." Integrating the internal setup times and the external setup times will increase the manufacturing productivity. Yazdani and his teamwork developed a branch-and- bound algorithm along with a lower bound and Repeated Solutions Identifier (RSI). The branch-and- bound algorithm counts the possible sequences of the board groups and observes for the best sequence among them. The branch-and- bound algorithm will also reduce the makespan objective for sequencing board groups made of several board types. The lower bound developed allows to avoid "non-promising solutions." The main purpose of the RSI approach is to filter out repeated solutions.